## **RTL9310**

LAYER 2/3 MANAGED 48\*10/100M/1000M + 6\*10GE -PORT SWITCH CONTROLLER

**Developer Guide**

Rev. 1.00 25 July 2018

Realtek Semiconductor Corp.

No. 2, Innovation Road II, Hsinchu Science Park, Hsinchu 300, Taiwan

Tel.: +886-3-578-0211 Fax: +886-3-577-6047

www.realtek.com

#### COPYRIGHT

©2018 Realtek Semiconductor Corp. All rights reserved. No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language in any form or by any means without the written permission of Realtek Semiconductor Corp.

#### **TRADEMARKS**

Realtek is a trademark of Realtek Semiconductor Corporation. Other names mentioned in this document are trademarks/registered trademarks of their respective owners.

#### **DISCLAIMER**

Realtek provides this document "as is", without warranty of any kind, neither expressed nor implied, including, but not limited to, the particular purpose. Realtek may make improvements and/or changes in this document or in the product described in this document at any time. This document could include technical inaccuracies or typographical errors.

#### USING THIS DOCUMENT

This document is intended for use by the system engineer when integrating with Realtek switch products. Though every effort has been made to assure that this document is current and accurate, more information may have become available subsequent to the production of this guide. In that event, please contact your Realtek representative for additional information that may help in the development process.

| Revision | Release Date | Summary |     |     |

|----------|--------------|---------|-----|-----|

| 1.0      | 2018/07/25   | Initial | 100 | ,00 |

|          |              | 6       |     |     |

|          |              |         |     |     |

|          |              |         |     | 100 |

|          |              | 5       |     | 70  |

|          |              |         | -   |     |

## **Contents**

| 1   |       | rview                        | . 19 |

|-----|-------|------------------------------|------|

| 1.1 | Chi   | ip Family                    | 19   |

| 1.2 | Fea   | ature List                   | 19   |

| 1.3 |       | ritching Architecture        |      |

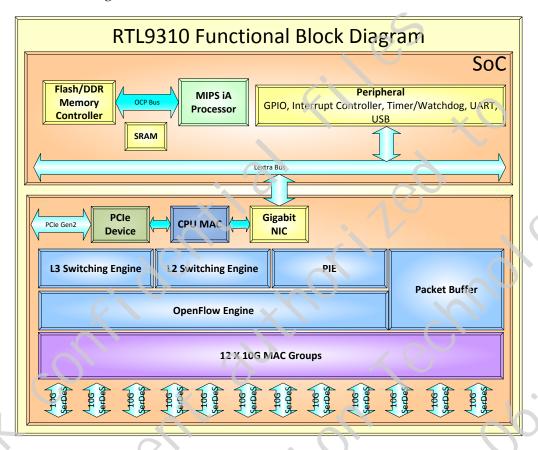

| 1.  | 3.1   | Device Block Diagram         |      |

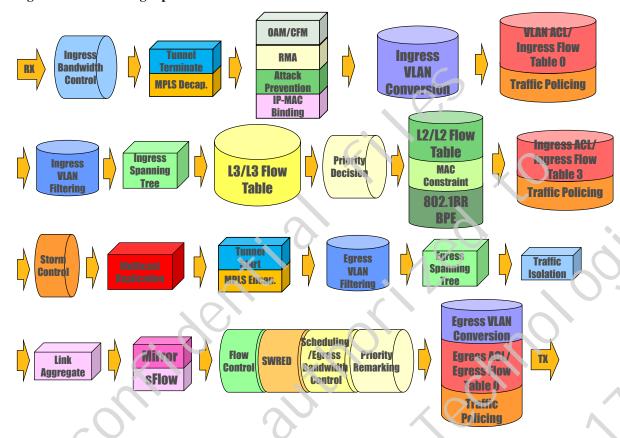

| 1.  | 3.2   | Pipeline WalkThrough         | 24   |

| 2   | VLAI  | N                            | . 26 |

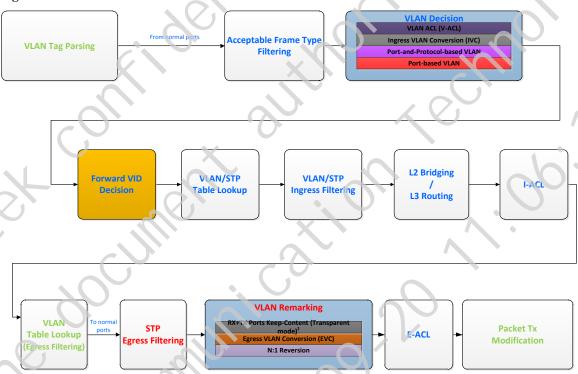

| 2.1 | VL/   | AN Overview                  |      |

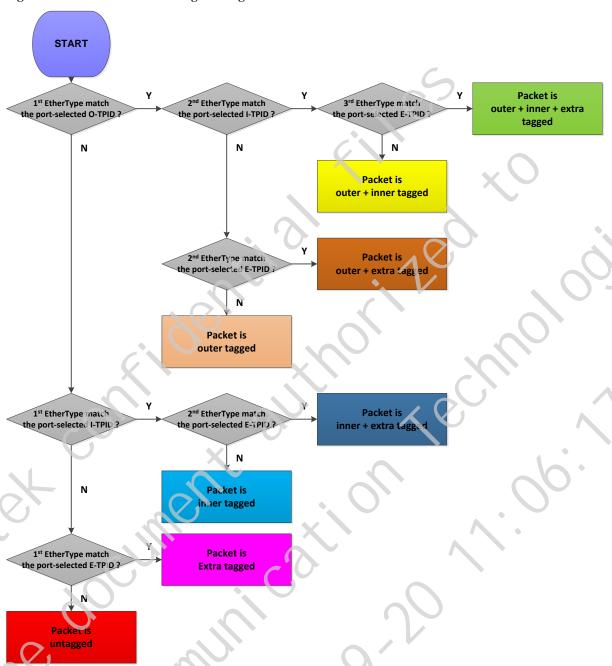

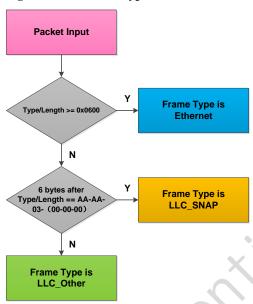

| 2.  | 1.1   | Tag parsing                  | 27   |

| 2.  | 1.2   | Accentable Frame Type        | 28   |

| 2.  | 1.3   | CFI Operation                | . 29 |

| 2.2 | VLA   | AN Assignment                | 29   |

|     | 2.1   | Port-based VLAN              | 31   |

| 2.  | 2.2   | Protocol-and-Port-based VLAN | 31   |

| 2.  | 2.3   | Ingress VLAN translation     | 32   |

| 2.  | 2.4   | MAC-based VLAN               | 35   |

| 2.  | 2.5   | IP Subnet-based VLAN         | 36   |

| 2.3 | VLA   | AN Forwarding and Filtering  | 37   |

|     | 3.1   | Forwarding VID Decision      | . 37 |

| 2.  | 3.2   | VLAN Table Format            | 38   |

| 2.  | 3.3   | VLAN Ingress Filter          | 39   |

| 2.  | 3.4   | VLAN-Egress Filter           | 39   |

| 2.  | 3.5   | VLAN profile                 | 40   |

| 2.  | 3.6   | VLAN application trap        | 41   |

| 2.4 | Egr   | ress VLAN translation        | 43   |

| (2. | 4.1   | Egress VID range check       | 45   |

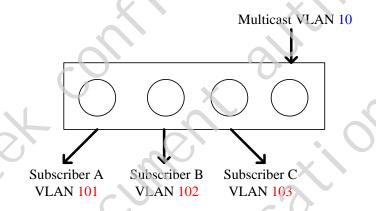

| 2.5 |       | 1 VLAN Aggregation           |      |

| 2.6 | Egr   | ress VLAN Tagging            | 47   |

| 2.  | 6.1   | Egress VLAN Mode             |      |

|     | 6.2   | Egress VLAN Tagging          | 48   |

| 2.  | 6.3   | Egress VLAN Tagging TPID     | 48   |

| 3   | L2 Sv | witch & Bridge               | . 49 |

| 3.1 | L2 :  | Switch                       | 49   |

| 3.  | 1.1   | Layer2 Forwarding            |      |

| 3.  | 1.2   | Address Entry Format         | 49   |

| 3.  | 1.3   | SA Look Up & SA Learning     | 51   |

| _   | 1.4   | DA Look Up                   | 56   |

|     | 1.5   | Age & Flush                  |      |

|     | 1.6   | MAC Constraint               |      |

|     | 1.7   | Source Port Filter           |      |

|     |       | L2 Notification              |      |

|     |       | anning Tree                  |      |

| 3.2.1  | Spanning Tree State Configuration   | 67   |

|--------|-------------------------------------|------|

| 3.2.2  | Spanning Tree Instance              |      |

|        | affic Isolation                     |      |

| 3.3.1  | Traffic Isolation Overview          |      |

| 3.3.2  | Port-based Isolation                |      |

| 3.3.3  | VLAN-based Isolation                |      |

|        | unk                                 | 72   |

| 3.4.1  | Overview                            |      |

| 3.4.2  | Stand-Alone And Stacking Trunk Mode |      |

| 3.4.3  | Normal Port Trunk                   |      |

| 3.4.4  | Stacking Port Trunk                 |      |

|        | served Multicast Address (RMA)      |      |

| 3.5.1  | RMA Overview                        | 79   |

| 3.5.2  | RMA OverviewRMA Entry               | 70   |

| 3.5.2  | User Defined RMA                    | - 06 |

| 3.5.4  | RMA Entry Action                    |      |

| 3.5.5  | STP Ingress Check Bypass            | 07   |

|        | VLAN Check Bypass                   |      |

| 3.5.6  | Cancel Mirror                       |      |

| 3.5.7  | SA Learning                         | 88   |

| 3.5.8  |                                     |      |

| 4 L3 F | eature                              | 90   |

| 4.1 Ro | uting                               | 90   |

| 4.1.1  | Routing Overview                    | 90   |

| 4.1.2  | L3 Interface                        | 90   |

| 4.1.3  | IP Unicast Routing                  |      |

| 4.1.4  | IP Multicast Bridging and Routing   | 107  |

| 4.2 Tu | nneling                             | 120  |

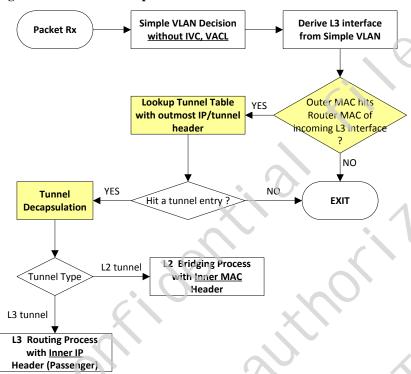

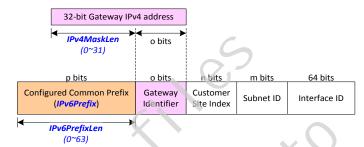

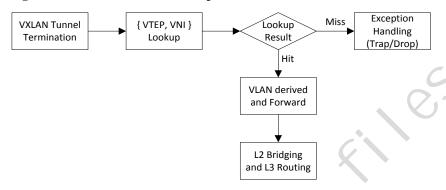

| 4.2.1  | Tunnel Decapsulation                |      |

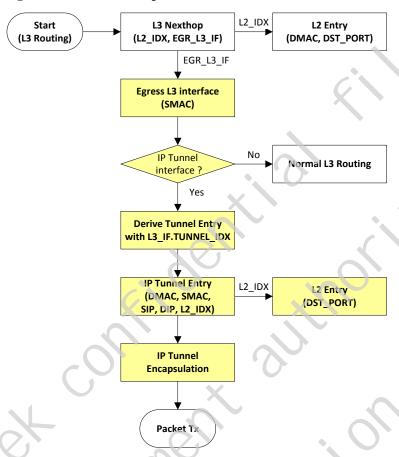

| 4.2.2  | Tunnel Encapsulation                | 126  |

|        |                                     |      |

| 5 MPI  | LS                                  | 130  |

| 5.1 M  | PLS Overview                        | 130  |

|        | PLS Decapsulation                   |      |

| 5.2.1  | Packet Processing Flow              | 131  |

|        | TTL & TC                            | 132  |

| 5.2.3  |                                     | 132  |

| 5.2.4  | Exception Handle                    | 132  |

| 5.3 MI | PLS Encapsulation                   | 133  |

| 5.3.1  | Packet Processing Flow              | 134  |

| 5.3.2  | TTL & TC                            |      |

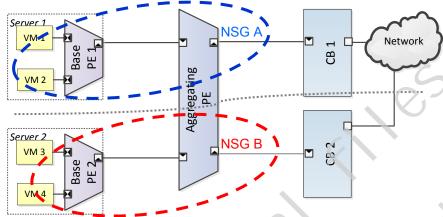

| 6 BPE  | tended Bridge                       | 125  |

| 6.1 Ex | tondad Bridge                       | 125  |

|        | Extended Bridge Port Configuration  |      |

| 6.1.1  |                                     |      |

| 6.1.2  | Name Space Group                    |      |

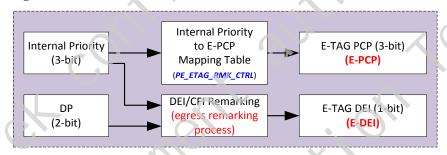

|        | Remark E-PCP and E-DEI              |      |

| 6.1.4  | PVID                                | 141  |

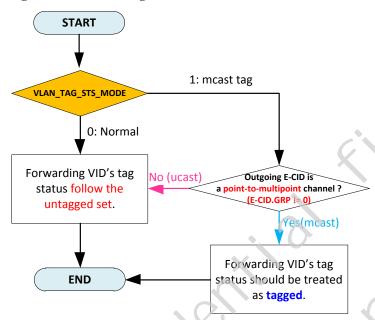

| 6.1.5  | Egress VLAN Tag Decision                 | 141 |

|--------|------------------------------------------|-----|

| 6.2 BF | PE Packet Process                        | 142 |

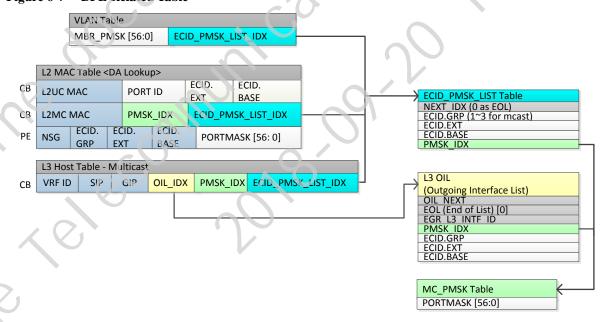

| 6.2.1  | BPE L2 Unicast Flow                      | 143 |

| 6.2.2  | BPE L2 Multicast Flow                    | 145 |

| 7 Qo   | s                                        | 147 |

| 7.1 Pr | iority and Drop Precedence Decision      | 147 |

| 7.1.1  | Priority Assignment                      | 147 |

| 7.1.2  | Priority Selection                       | 153 |

| 7.1.3  | RSPAN Priority                           | 156 |

| 7.1.4  | Internal Priority to QID Mapping         |     |

| 7.1.5  | Drop Precedence Assignment               | 158 |

| 7.1.6  | Drop Precedence Selection                |     |

| 7.2 Sc | cheduling Algorithm                      |     |

| 7.2.1  | Strict Priority                          |     |

| 7.2.2  | Weighted Round Robin                     | 162 |

| 7.2.3  | Weighted Fair Queue                      | 163 |

| 7.3 Eg | gress Remarking                          | 163 |

| 7.3.1  | Inner-tag Priority Remarking             | 164 |

| 7.3.2  | Outer-tag Priority Remarking             | 166 |

| 7.3.3  | DSCP Remarking                           | 168 |

| 7.3.4  | DEI Remarking                            | 170 |

| 8 Tra  | ffic Suppression & Rate Limit            | 172 |

| 8.1 In | gress Bandwidth Control                  | 172 |

| 8.1.1  | Bandwidth Configuration                  |     |

| 8.1.2  | Protocol Bypass                          |     |

|        | gress Bandwidth                          |     |

| 8.2.1  |                                          |     |

| 8.2.2  | Egress Queue Bandwigth Management        |     |

| 8.2.3  | CPU Port Egress Bandwidth Management     |     |

|        | orm Control                              |     |

| 8.3.1  | Basic Storm Control                      |     |

| 8.3.2  | Storm Control Bypass Mechanism.          |     |

| 833    | Protocol Storm Control                   | 181 |

| 8.4 M  | leter                                    | 184 |

| 8.4.1  | Meter Overview                           | 184 |

| 8.4.2  | Dual Leaky Bucket (D'.B)                 | 185 |

| 8.4.3  | Single Rate Three Color Marker (srTCM)   | 185 |

| 8.4.4  | Two Rate Three Color Marker (trTCM)      |     |

| 8.4.5  | Exceed Flag                              | 186 |

| 9 Buf  | fer Management                           | 187 |

|        | mplified Weighted Random Early Detection |     |

| 9.1.1  | Threshold Configuration                  |     |

| 9.1.2  | Drop Mechanism                           |     |

| ~      | ess Control List                         |     |

|        |                                          |     |

| TULI A | CL                                       | 190 |

### RTL9310 Developer Guide

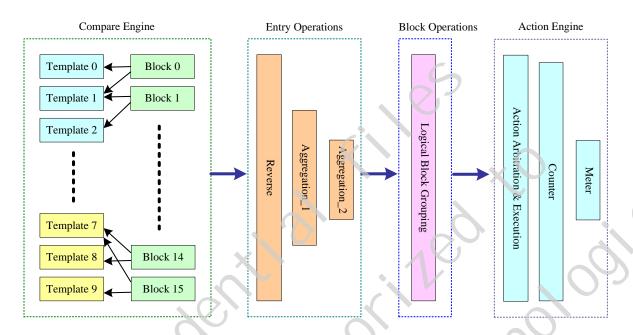

| 10.1.1     | ACL Overview               | 190        |

|------------|----------------------------|------------|

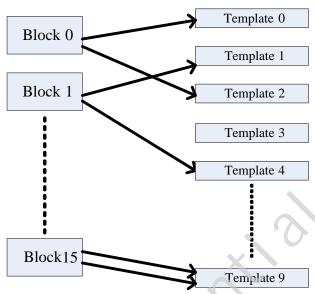

| 10.1.2     | PIE Block                  | 191        |

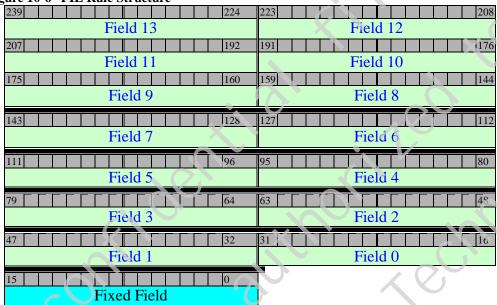

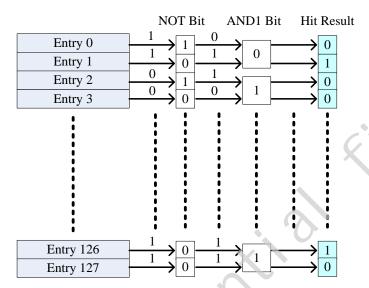

| 10.1.3     | PIE Rule Template          | 192        |

| 10.1.4     | PIE Rule                   | 205        |

| 10.1.5     | ACL Action                 | 209        |

| 10.1.6     | ACL Clearance and Movement | 222        |

| 10.2 Field | d Selector                 | 223        |

| 10.2.1     | Overview                   | 223        |

| 11 CDIII   | Interface                  |            |

| 11 CPU     | Interrace                  | 225        |

|            |                            |            |

| 11.1.1     |                            | 225        |

| 11.1.2     | Transmit                   | 226        |

|            |                            | 228        |

| 11.2.1     | RX CPU Tag                 |            |

| 11.2.2     | TX CPU Tag                 | 232        |

| 11.2.3     | Queuing to CPU             | 235        |

| 11.2.4     |                            | 235        |

| 12 Social  | rita                       | 220        |

| 12 Secui   | al. Dravantian             |            |

|            | ick Prevention             | 238        |

| 12.1.1     | Overview                   |            |

| 12.1.2     | Attack Detection           |            |

| 12.1.3     | validation Check           | 242        |

|            |                            | 243        |

| 12.2.1     | Binding Table              | 243        |

| 12.2.2     | Binding Validation Process | 244        |

| 13 Netw    | york Monitor               | <b>246</b> |

| 13.1 Mir   | or                         | 246        |

| 13.1.1     | Overview                   |            |

| 12.1.1     | Port Paced Mirror          | 246        |

| 13.1.2     | Flow Passe Mirror          | 246<br>247 |

|            | DCDAN                      | 247        |

| 13.1.4     | Misses Ontion              | 248        |

| 13.1.5     | Canalia a                  | 250        |

| 13.1.6     |                            |            |

|            |                            | 254        |

| 13.2.1     | sFlow Overview             | 254        |

| 13.2.2     | sFlow Sampling Method      | 254        |

| 13.2.3     |                            | 255        |

| 14 Diagr   | nostic                     | 256        |

| 14.1 OAN   | 1                          | 256        |

| 14.1.1     |                            | 256        |

| 14.1.2     |                            | 256        |

| 14.1.2     | •                          |            |

|            | <b>y</b> , <b>c</b> ,      |            |

|            |                            |            |

| 14.2.1     |                            |            |

| 14.2.2     | CCIVI RECEPTION            | 260        |

| 14.3 ETH- | ·DM                         |      | 261        |

|-----------|-----------------------------|------|------------|

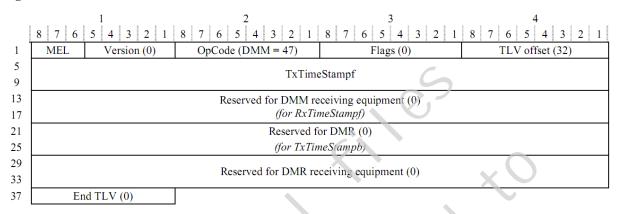

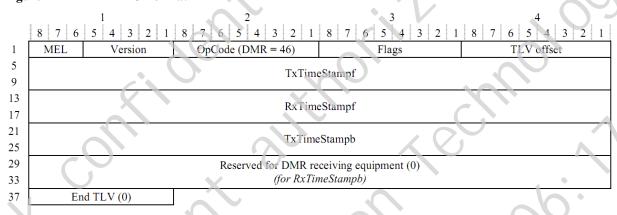

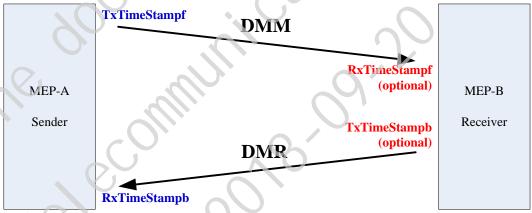

| 14.3.1    | Overview                    |      | 261        |

| 14.3.2    | ETH-DM Time Clock Module    |      | 264        |

| 14.3.3    | RX Timestamp Recording      |      | 264        |

| 15 C+-al- | ·                           | 6    | 200        |

| 15 Stack  |                             |      |            |

|           | _                           |      |            |

|           |                             |      |            |

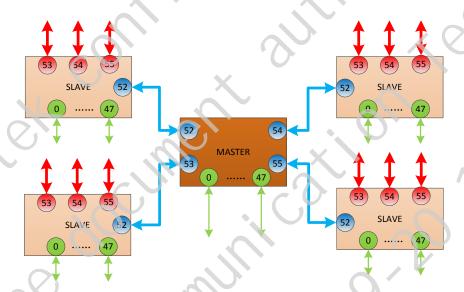

| 15.2.1    | Star lopology               |      | 266        |

| 15.2.2    |                             |      |            |

| 15.2.3    | Ring Topology               |      | 267        |

|           |                             |      |            |

| 15.3.1    | Device ID                   |      | 267        |

| 15.3.2    | Stacking Port               |      | 267        |

| 15.3.3    | One-Hop Path                |      | 267        |

| 15.3.4    | Stacking Port Trunk         |      | 268        |

| 15.3.5    | Loop Prevention             |      | 268        |

|           | Plane                       |      | 269        |

| 15.4.1    |                             |      |            |

| 15.4.2    | Multicast Bridging          |      | 271        |

| 15.4.3    | Broadcast Bridging          |      | 272        |

| 15.4.4    | Unicast Routing             |      | 272        |

| 15.4.5    |                             |      |            |

| 15.5 Cont | rol Plane                   |      | 273        |

| 15.5.1    | Device Talk                 | X    | 273        |

| 15.5.2    | Control Packet              |      | 275        |

| 15.6 Stac | king Port QoS               |      | 275        |

| 15.6.1    | Data Plane                  |      | 275        |

| 15.6.2    | Control Plane               |      | 276        |

| 15.6.3    | TX Timestamp Writing        |      | 278        |

| 16 Open   | Elow                        |      | 270        |

|           | riow                        |      | <b>2/3</b> |

| 16.1 Feat | Table Consolition Supersons |      | 279        |

| 16.2 FIOW | riable Capability Summary   |      | 2/9        |

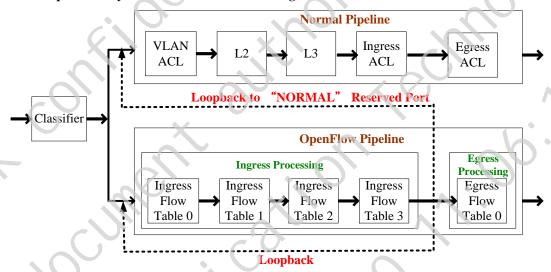

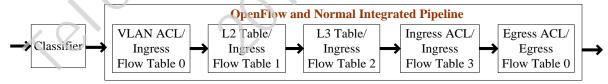

| 16.3 Pipe | line Processing             |      | 280        |

|           |                             | sing |            |

| 16.3.2    |                             |      |            |

|           | Viaten Flow Table           |      | 282        |

| 16.4.1    |                             |      |            |

| 16.4.2    | Match Field                 |      | 283        |

| 16.4.3    |                             |      |            |

| 16.4.4    |                             |      |            |

| 16.4.5    | . 3                         | 5    |            |

| 16.4.6    |                             |      |            |

| 16.4.7    |                             |      |            |

| 16.4.8    |                             |      |            |

| 16.5 L2 O | ntimized Flow Table         |      | 297        |

| 16.5.1    | •                           |      |            |

#### RTL9310 Developer Guide

| 16.5.2     | L2 Flow Entry Match Field    |     | 298 |

|------------|------------------------------|-----|-----|

| 16.5.3     | L2 Flow Entry Instructions   |     | 300 |

| 16.5.4     | L2 Flow Entry Hash Algorithm |     |     |

| 16.6 L3 O  | ptimized Flow Table          |     |     |

| 16.6.1     | L3 TCAM-based Flow Entry     |     |     |

| 16.6.2     | L3 Hash-based Flow Entry     |     |     |

| 16.6.3     | L3 Flow Entry Instructions   |     |     |

| 16.6.4     | L3 Flow Entry Hit Indication |     |     |

| 16.6.5     | L3 Flow Entry Hash Algorithm |     |     |

| 16.6.6     | L3 Flow Entry Capacity       |     | 309 |

| 16.7 Table | Miss                         |     |     |

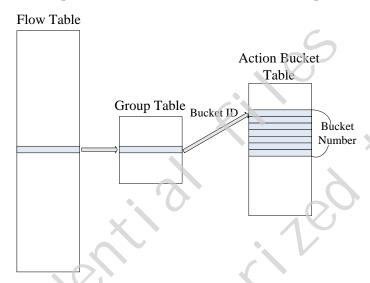

|            | p Table                      |     |     |

| 16.8.1     | Group Entry Hash Algorithm   |     | 311 |

| 16.8.2     | Action Bucket Table          | , U | 312 |

|            | Counters                     |     |     |

|            |                              |     |     |

## **Table List**

| Table 1-1  | Family Member List                                                                            | 19   |

|------------|-----------------------------------------------------------------------------------------------|------|

| Table 1-2  | Feature List                                                                                  | 19   |

| Table 2-1  | VLAN_PORT_AFT Register                                                                        | 29   |

| Table 2-2  | VLAN_PORT_AFT Register                                                                        | 29   |

| Table 2-3  | VLAN_PORT_PB_VLAN Register                                                                    | 31   |

| Table 2-4  | VLAN PPB VLAN SET Entry Format                                                                | 31   |

| Table 2-5  | VIAN PORT PPR VIAN SET Entry Format                                                           | 32   |

| Table 2-6  | IVC Search Key  IVC Action List  VLAN_IGR_VID_RNG_CHK_SET Register  MAC-based VLAN Search Key | 32   |

| Table 2-7  | IVC Action List                                                                               | 33   |

| Table 2-8  | VLAN_IGR_VID_RNG_CHK_SFT Register                                                             | 35   |

| Table 2-9  | MAC-based VLAN Search Key                                                                     | 35   |

| Table 2-10 | MAC-based VLAN Action list                                                                    | 35   |

| Table 4-11 | IP Subnet-based VLAN Search Key                                                               | 36   |

| Table 2-11 | IP Subnet-basec' VLAN Search Key  VLAN_PORT_FWD_CTRL Register  VLAN Table Entry               | 37   |

| Table 2-12 | VLAN Table Entry                                                                              | 38   |

| Table 2-13 | VLAN_PORT_IGR_FLTR Register                                                                   | 39   |

| Table 2-14 | VLAN_PORT_EGR_FLTR Register VLAN_PORT_EGR_FLTR Register                                       | 39   |

| Table 2-15 | VLAN_CTRL Register                                                                            | . 39 |

| Table 2-16 | VLAN PROFILE SET Register                                                                     | 40   |

| Table 2-17 | VLAN_APP_PKT_CTRL Register                                                                    | 41   |

| Table 2-18 | Application Trap Application Trap                                                             | 42   |

| Table 2-19 | EVC Search Key                                                                                | 43   |

| Table 2-20 | EVC Action List                                                                               | 44   |

| Table 2-21 | VLAN_EGR_VID_RNG_CHK_SET Register                                                             | 45   |

| Table 2-22 | VLAN_PORT_L2TBL_CNVT_CTRL Register                                                            | 46   |

| Table 2-23 | VLAN_TRUNK_L2TBL_CNVT_CTRL Register                                                           | 46   |

| Table 2-24 | VLAN_PORT_TAG_STS_CTRL Register                                                               | 47   |

| Table 2-25 | VLAN PORT TAG STS CTRL Register                                                               | 48   |

| Table 3-1  | L2 Entry Format                                                                               | 49   |

| Table 3-2  | L2 Unicast Table Entry                                                                        | 50   |

| Table 3-3  | L2 Multicast Table Entry                                                                      | 50   |

| Table 3-4  | Port-mask Table Entry                                                                         | 51   |

| Table 3-5  | L2_CTRL Register                                                                              | 51   |

| Table 3-6  | L2_PORT_SALRN Register                                                                        | 52   |

| Table 3-7  | VLAN_PROFILE_SET Register                                                                     | 52   |

| Table 3-8  | L2_SA_ACT_REF Register                                                                        | 52   |

| Table 3-9  | 12_PORT_NEW_SA_FWD Register                                                                   | 53   |

| Table 3-10 | VLAN_PROFILE_SET Register                                                                     | 53   |

| Table 3-11 | L2_ PORT_DYN_MV_ACT Register                                                                  | 54   |

| Table 3-12 | L2_PORT_DYN_MV_LRN Register                                                                   | 54   |

| Table 3-13 | L2_GLB_STT_PORT_MV_ACT Register                                                               | 54   |

| Table 3-14 | L2_GLB_STT_PORT_MV_LRN Register                                                               | 54   |

| Table 3-15 | L2_PORT_MV_FORBID Register                                                               | 54 |

|------------|------------------------------------------------------------------------------------------|----|

| Table 3-16 | L2_TRK_MV_FORBID Register                                                                | 55 |

| Table 3-17 | L2_PORT_MV_FORBID_CTRL Register                                                          | 55 |

| Table 3-18 | L2_PORT_SABLK_CTRL Register                                                              | 55 |

| Table 3-19 | 12 CTRI Register                                                                         | 56 |

| Table 3-20 | L2_PORT_UC_LM_ACT Register                                                               | 56 |

| Table 3-21 | L2_PORT_UC_LM_ACT Register                                                               | 56 |

| Table 3-22 | L2 Entry Format                                                                          | 56 |

| Table 3-23 | L2 PORT DABLK CTRL Register                                                              | 57 |

| Table 3-24 | L2 Entry Format                                                                          | 57 |

| Table 3-25 | VLAN_PROFILE_SET Register                                                                | 57 |

| Table 3-26 | L2_BC_FLD_PMSK Register                                                                  | 58 |

| Table 3-27 | L2_PORT_AGE_CTRL Register                                                                | 59 |

| Table 3-28 | L2_TRK_AGE_CTRL Register                                                                 | 59 |

| Table 3-29 | L2_AGE_CTRL Register                                                                     | 59 |

| Table 3-30 | L2_PORT_AGE_CTRL Register L2_TRK_AGE_CTRL Register L2_AGE_CTRL Register L2_CTRL Register | 59 |

| Table 3-31 | L2 TBL FLUSH CTRL Register                                                               | 59 |

| Table 3-32 | L2_LRN_CONSTRT_CTRL RegisterL2_LRN_CONSTRT_CNT Register                                  | 61 |

| Table 3-33 | L2_LRN_CONSTRT_CNT Register                                                              | 61 |

| Table 3-34 | L2_LRN_PORT_CONSTRT_CTRL & L2_LRN_TRK_CONSTRT_CTRL Register                              |    |

| Table 3-35 | L2_LRN_PORT_CONSTRT_CNT/ & L2_LRN_TRK_CONSTRT_CNT Register                               |    |

| Table 3-36 | L2_LRN_VLAN_CONSTRT_ENTRY Register                                                       | 62 |

| Table 3-37 | L2 LRN VLAN CONSTRT CNT Register                                                         | 62 |

| Table 3-38 | L2_VLAN_CONSTRT_CTRL Register                                                            | 62 |

| Table 3-39 | L2_SRC_P_FLTR Register                                                                   | 62 |

| Table 3-40 | L2_SRC_P_FLTR Register                                                                   | 63 |

| Table 3-41 | Descriptor Entry Format                                                                  |    |

| Table 3-42 | NBuf Entry Format                                                                        |    |

| Table 3-43 | L2_NTFY_RING_CUR_ADDR Register                                                           | 65 |

| Table 3-44 | L2_NTFY_IF_INTR_STS Register                                                             | 65 |

| Table 3-45 | L2_NTFY_NIC_FIFO_STS Register                                                            | 66 |

| Table 3-46 | L2_NTFY_NIC_FIFO_STS Register L2_NTFY_PKT_MAC Register L2_NTFY_PKT_MAGIC_NUM Register    | 67 |

| Table 3-47 | L2_NTFY_PKT_MAGIC_NUM Register                                                           | 67 |

| Table 3-48 | L2_NTFY_PKT_CTRL RegisterL2_NTFY_PKT_TIMEOUT Register                                    | 67 |

| Table 3-49 | L2_NTFY_PKT_TIMEOUT Register                                                             | 67 |

| Table 3-50 | Definition of FCS                                                                        | 67 |

| Table 3-51 | Port State Description                                                                   | 68 |

| Table 3-52 | Port State Description                                                                   | 69 |

| Table 3-53 | ST_CTRL Register                                                                         | 69 |

| Table 3-54 | PORT_ISO_CTRL Register                                                                   |    |

| Table 3-55 | PORT_ISO_RESTRICT_ROUTE_CTRL Register                                                    |    |

| Table 3-56 | PORT_ISO_VB_ISO_PMSK_CTRL Register                                                       |    |

| Table 3-57 | TRK_CTRL Register                                                                        |    |

| Table 3-58 | Differences of Stand-Alone and Stacking Mode                                             |    |

| Table 3-59 | Source Port Mapping Table Entry                                                          |    |

| Table 3-60 | TRK_ID_CTRL Register                                                                     |    |

| Table 3-61 | TRK_MBR_CTRL Register                                                                    | 73 |

| Table 3-62 | Egress Trunk Table Entry                                                      | 74  |

|------------|-------------------------------------------------------------------------------|-----|

| Table 3-63 | Hash Key                                                                      |     |

| Table 3-64 | TRK_HASH_CTRL Register                                                        | 76  |

| Table 3-65 | PROTO Hash Key Original                                                       | 76  |

| Table 3-66 | PROTO Hash Key Shifted                                                        | 76  |

| Table 3-67 | TRK SHFT CTRL Register                                                        | 76  |

| Table 3-68 | TRK_SHFT_CTRL Register TRK_CTRL Register                                      | 77  |

| Table 3-69 | TRK_CTRL Register                                                             | 78  |

| Table 3-70 | TRK_STK_CTRL Register                                                         | 78  |

| Table 3-71 | RMA_PORT_BPDU_CTRL                                                            | 79  |

| Table 3-72 | RMA_PORT_PTP_CTRL                                                             | 80  |

| Table 3-73 | PMA DOPT LIND CTPI                                                            | 90  |

| Table 3-74 | RMA PORT EAPOL CTRL                                                           | 80  |

| Table 3-75 | RMA CTRL 0                                                                    | 81  |

| Table 3-76 | RMA CTRL 1                                                                    | 82  |

| Table 3-77 | RMA CTRL 2                                                                    | 84  |

| Table 3-78 | RMA_PORT_EAPOL_CTRLRMA_CTRL_0 RMA_CTRL_1 RMA_CTRL_2 RMA_USR_DEF_CTRL Register | 86  |

| Table 3-79 | RMA MIRROR CTRL Register                                                      | 88  |

| Table 3-80 | RMA_MIRROR_CTRL Register                                                      | 89  |

| Table 3-81 | RMA MGN LRN CTRL Register                                                     | 89  |

| Table 4-1  | 13 HOST ROUTE IPUC Entry                                                      | 92  |

| Table 4-2  | L3_NEXTHOP Table                                                              | 100 |

| Table 4-3  | L3_NEXTHOP Table                                                              | 102 |

| Table 4-4  | ECMP Table                                                                    | 103 |

| Table 4-5  | VLAN_PROFILE_SET Register                                                     | 108 |

| Table 4-6  | VLAN_PROFILE_SET Register                                                     | 110 |

| Table 4-7  | L3_IPMC_ROUTE_CTRL Register                                                   |     |

| Table 4-8  | L3_IP6MC_ROUTE_CTRL Register                                                  | 110 |

| Table 4-9  | IPMC Entry                                                                    |     |

| Table 4-10 | L3_EGR_INTF_LIST (Multicast Outing Interface List) Entry                      | 113 |

| Table 4-11 | L3_MONT_CNTR_CTRL Register                                                    | 115 |

| Table 4-12 | L3_MONT_CNTR_DATA Register                                                    | 116 |

| Table 4-13 | L3_IPMC_ROUTE_CTRL Register                                                   | 116 |

| Table 4-14 | L3_IP6MC_ROUTE_CTRL Register                                                  | 116 |

| Table 4-15 | L3_IPMC_ROUTE_CTRL Register                                                   | 117 |

| Table 4-16 | L3_IP6MC_ROUTE_CTRL Register                                                  | 117 |

| Table 4-17 | L3_IPMC_ROUTE_CTRL Register                                                   | 117 |

| Table 4-18 | L3_IP6MC_ROUTE_CTRL Register                                                  | 118 |

| Table 4-19 | L3_IPMC_ROUTE_CTRL Register                                                   | 119 |

| Table 4-20 | L3_IP6MC_ROUTE_CTRL Register                                                  | 119 |

| Table 4-21 | L3_IPMC_ROUTE_CTRL Register                                                   | 119 |

| Table 4-22 | L3_IP6MC_ROUTE_CTRL Register                                                  | 120 |

| Table 4-23 | Supported Tunnel Types                                                        | 120 |

| Table 4-24 | Decapsulation-related Tunnel Interface Configuration                          | 122 |

| Table 4-25 | Encapsulation-related Tunnel Interface Configuration                          | 127 |

| Table 5-1  | TC behavior                                                                   | 132 |

| Table 5-2  | E-LSP and L-LSP behavior                                                      | 132 |

| Table 5-3  | MPLS_GLB_CTRL Register                                                                        | 132        |

|------------|-----------------------------------------------------------------------------------------------|------------|

| Table 5-4  | MPLS_GLB_CTRL Register                                                                        | 132        |

| Table 5-5  | MPLS_GLB_CTRL Register                                                                        | 133        |

| Table 6-1  | PE_ETAG_MAC_CTRL Register                                                                     |            |

| Table 6-2  | PE_PORT_ETAG_MAC_CTRL Register                                                                | 137        |

| Table 6-3  | PE_PORT_ETAG_IGR_CTRL Register                                                                | 137        |

| Table 6-4  | PE_PORT_ETAG_EGR_CTRL Register                                                                | 137        |

| Table 6-5  | PE_PORT_PCID_CTRL Register                                                                    | 138        |

| Table 6-6  | Example for CB Port Configuration                                                             | 138        |

| Table 6-7  | Example for Common PE Port Configuration                                                      | 139        |

| Table 6-8  | Example for Aggregating PE Port Configuration                                                 | 140        |

| Table 6-9  | Example for Base PE Port Configuration                                                        | 140        |

| Table 6-10 | L2_UNKN_UC_FLD_PMSK Register                                                                  | 144        |

| Table 6-11 | L2_CTRL Register                                                                              | 144        |

| Table 6-12 | L2_CTRL Register                                                                              | 144        |

| Table 7-1  | L2_UNKN_UC_FLD_PMSK Register  L2_CTRL Register  L2_CTRL Register  PRI_SEL_REMAP_PORT Register | 148        |

| Table 7-2  | PRI_SEL_CIRL Register                                                                         | 148        |

| Table 7-3  | PRI_SEL_PORT_CTRL Register                                                                    | 149        |

| Table 7-4  | PRI_SEL_REMAP_DSCP Register                                                                   |            |

| Table 7-5  | PRI_SEL_CTRL Register – Invalid DSCP Relative Configuration                                   | 149        |

| Table 7-6  | PRI_SEL_REMAP_IPRI_CFIO Register                                                              | 150        |

| Table 7-7  | PRI_SEL_REMAP_IPRI_CFI1_Register                                                              | 150        |

| Table 7-8  | PRI SEL REMAP OPRI DEIO Register                                                              | 151        |

| Table 7-9  | PRI_SEL_REMAP_OPRI_DEI1 Register                                                              |            |

| Table 7-10 | PRI_SEL_CTRL Register - MAC-based/IP-subnet-based Priority Relative Con                       | figuration |

|            | 151                                                                                           |            |

| Table 7-11 | PRI_SEL_CTRL Register – Protocol-and-port-based Priority Relative Configu                     |            |

| Table 7-12 | PRI_SEL_REMAP_1BR Register                                                                    |            |

| Table 7-13 | PRI_SEL_REMAP_MPLS Register                                                                   | 153        |

| Table 7-14 | PRI_SEL_PORT_TBL_IDX_CTRL Register                                                            |            |

| Table 7-15 | PRI_SEL_TBL_CTRL Register                                                                     | 154        |

| Table 7-16 | QM_INTPRI2QID_CTRL Register                                                                   | 156        |

| Table 7-17 | OM_CPUQID2QID_CTRL Register                                                                   | 156        |

| Table 7-18 | QM_CPUQID2XGSQID_CTRL Register                                                                | 156        |

| Table 7-19 |                                                                                               | 156        |

| Table 7-20 | DP_SEL_REMAP_DSCP Register                                                                    |            |

| Table 7-21 | DP_SEL_REMAP_ITAG_CFI0 Register                                                               |            |

| Table 7-22 | DP_SEL_REMAP_ITAG_CFI1 Register                                                               |            |

| Table 7-23 | DP_SEL_REMAP_OTAG_DEI0 Register                                                               |            |

| Table 7-24 | DP_SEL_REMAP_OTAG_DEI1 Register                                                               |            |

| Table 7-25 | DP_SEL_REMAP_MPLS Register                                                                    |            |

| Table 7-26 | DP_SEL_PORT_TBL_CTRL Register                                                                 |            |

| Table 7-27 |                                                                                               |            |

| Table 7-28 | SCHED_PORT_ALGO_CTRL Register                                                                 |            |

| Table 7-29 | RMK_PORT_CTRL Register – Remarking Ability Relative Configuration                             |            |

| Table 7-30 | RMK_CTRL Register – Inner-priority Remarking Relative Configuration                           |            |

| Table 7-31 | RMK_INTPRI2IPRI_CTRL Register                                                                 | 165        |

| Table 7-32 | RMK_IPR2IPRI_CTRL Register                                                                                     | 165 |

|------------|----------------------------------------------------------------------------------------------------------------|-----|

| Table 7-33 | RMK_OPR2IPRI_CTRL Register                                                                                     | 165 |

| Table 7-34 | RMK_DSCP2IPRI_CTRL Register                                                                                    | 165 |

| Table 7-35 | REMARK Register – Default Inner-priority Relative Configuration                                                | 166 |

| Table 7-36 | RMK_CTRL Register – Outer-priority Remarking Relative Configuration                                            | 166 |

| Table 7-37 | RMK_INTPRI2OPRI_CTRL Register                                                                                  |     |

| Table 7-38 | RMK_IPR2OPRI_CTRL Register                                                                                     | 167 |

| Table 7-39 | RMK_OPR2OPRI_CTRL Register                                                                                     |     |

| Table 7-40 | RMK_DSCP2OPRI_CTRL Register                                                                                    | 167 |

| Table 7-41 | REMARK Register – Default Outer-priority Relative Configuration                                                |     |

| Table 7-42 | RMK_CTRL Register – Outer-priority Remarking Relative Configuration                                            |     |

| Table 7-43 | RMK_INTPRI2DSCP_CTRL Register                                                                                  | 168 |

| Table 7-44 | RMK IPR2DSCP CTRL Register                                                                                     | 169 |

| Table 7-45 | RMK_IPR2DSCP_CTRL RegisterRMK_OPR2DSCP_CTRL RegisterRMK_DSCP2DSCP_CTRL RegisterRMK_DPINTPRI2DSCP_CTRL Register | 169 |

| Table 7-46 | RMK_DSCP2DSCP_CTRL Register                                                                                    | 169 |

| Table 7-47 | RMK DPINTPRI2DSCP CTRL Register                                                                                | 169 |

| Table 7-48 | RMK_PORT_CTRL Register – DEI Remarking Relative Configuration                                                  | 170 |

| Table 7-49 | RKM CTRL Register – DEI Remarking Relative Configuration                                                       | 170 |

| Table 7-50 | RMK_INTPRI2DEI_CTRL RegisterRMK_DP2DEI_CTRL Register                                                           | 171 |

| Table 7-51 | RMK DP2DEI CTRL Register                                                                                       | 171 |

| Table 8-1  | IGBW PORT CTRL Register                                                                                        | 173 |

| Table 8-2  | IGBW_PORT_CTRL Register IGBW_PORT_EXCEED_FLAG Register IGBW_PORT_FC_CTRL Register                              | 173 |

| Table 8-3  | IGBW PORT FC CTRL Register                                                                                     | 173 |

| Table 8-4  | IGBW_CTRL Register                                                                                             | 174 |

| Table 8-5  | EGBW_CTRL Register                                                                                             | 175 |

| Table 8-6  | EGBW_PORT_CTRL Register                                                                                        | 175 |

| Table 8-7  | EGR_Q_BW Register                                                                                              | 176 |

| Table 8-8  | EGBW_CTRL Register                                                                                             |     |

| Table 8-9  | EGBW_CPU_MAX_LB_CTRL Register                                                                                  |     |

| Table 8-10 | STORM_PORT_UC_CTRL Register                                                                                    | 179 |

| Table 8-11 | STORM PORT MC CTRI Register                                                                                    | 170 |

| Table 8-12 | STORM_PORT_BC_CTRL Register                                                                                    | 179 |

| Table 8-13 | STORM_PORT_CTRL Register                                                                                       | 180 |

| Table 8-14 | STORM_PORT_UC_EXCEED_FLAG Register                                                                             | 180 |

| Table 8-15 |                                                                                                                |     |

| Table 8-16 | STORM_PORT_BC_EXCEED_FLAG Register                                                                             | 180 |

| Table 8-17 | STORM_CTRL Register                                                                                            |     |

| Table 8-18 | STORM_PORT_PROTO_BPDU_CTRL Register                                                                            |     |

| Table 8-19 | STORM PORT PROTO DHCP CTRL Register                                                                            | 182 |

| Table 8-20 | STORM PORT_PROTO_IGMP_CTRL Register                                                                            | 182 |

| Table 8-21 | STORM_PORT_PROTO_ARP_CTRL Register                                                                             | 182 |

| Table 8-22 | STORM PORT PROTO DHCP EXCEED FLAG Register                                                                     |     |

| Table 8-23 | STORM_PORT_PROTO_BPDU_EXCEED_FLAG Register                                                                     |     |

| Table 8-24 | STORM_PORT_PROTO_IGMP_EXCEED_FLAG Register                                                                     |     |

| Table 8-25 | STORM_PORT_PROTO_ARP_EXCEED_FLAG Register                                                                      |     |

| Table 8-26 | STORM_CTRL Register                                                                                            |     |

| Table 8-27 | Configuration of each entry in METER Table                                                                     |     |

|            |                                                                                                                |     |

| Table 8-28  | METER_GLB_CTRL Register                                                                   | 185 |

|-------------|-------------------------------------------------------------------------------------------|-----|

| Table 8-29  | METER_LB_EXCEED_STS Register                                                              | 186 |

| Table 8-30  | METER_LB_GLB_EXCEED_STS Register                                                          | 186 |

| Table 9-1   | FC_PORT_EGR_DROP_CTRL Register                                                            | 187 |

| Table 9-2   | SWRED_Q_THR Register SWRED_Q_DROP_RATE Register                                           | 187 |

| Table 9-3   | SWRED_Q_DROP_RATE Register                                                                | 187 |

| Table 10-1  | PIE_BLK_PHASE_CTRL Register                                                               | 191 |

| Table 10-2  | PIE_BLK_GROUP_CTRL Register                                                               | 192 |

| Table 10-3  | PIE_BLK_TMPLTE_CTRL Register                                                              | 192 |

| Table 10-4  | Pre-defined Template 0                                                                    |     |

| Table 10-5  | Pre-defined Template 1                                                                    |     |

| Table 10-6  | Pre-defined Template 2                                                                    | 193 |

| Table 10-7  | Pre-defined Template 3                                                                    | 193 |

| Table 10-8  | Pre-defined Template 4                                                                    | 194 |

| Table 10-9  | PIE_CTRL Register                                                                         | 194 |

| Table 10-10 | Pre-defined Template 3  Pre-defined Template 4  PIE_CTRL Register  PIE_TAG_CTRL Register  | 195 |

| Table 10-11 | Configurable Template Format                                                              | 195 |

| Table 10-12 | Definition of FCS                                                                         | 196 |

| Table 10-13 | PIE_MISC Register                                                                         | 203 |

| Table 10-14 | Definition of FCS PIE_MISC Register PARSER_CTRL Register PIE_RULE_HIT_INDICATION Register | 203 |

| Table 10-15 | PIE_RULE_HIT_INDICATION Register                                                          | 208 |

| Table 10-16 | PIE_GLB_HIT_INDICATION RegistersVACL Action Table Entry                                   | 208 |

| Table 10-17 | VACL Action Table Entry                                                                   | 209 |

| Table 10-18 | IACL Action Table Entry                                                                   | 216 |

| Table 10-19 | EACL Action Table Entry                                                                   | 220 |

| Table 10-20 |                                                                                           |     |

| Table 10-21 | PIE_MV_CTRL Register                                                                      |     |

| Table 10-22 | PIE_MV_LEN_CTRL Register                                                                  | 223 |

| Table 10-23 | PIE_FIELD_SELTOR_CTRL Register                                                            | 223 |

| Table 10-24 | PIE_FIELD_SELTOR_CTRL Register  Type of start position                                    | 224 |

| Table 11-1  | Descriptor Fields                                                                         | 226 |

| Table 11-2  | DMA_IF_CTRL Register                                                                      | 227 |

| Table 11-3  | Fields of CPU RX Tag                                                                      | 228 |

| Table 11-4  | DMA_IF_CTRL Register  Fields of CPU RX Tag  DMA_IF_PKT_CTRL Register                      | 232 |

| Table 11-5  | Fields of CPU TX Tag                                                                      | 232 |

| Table 11-6  | QM_RSN2CPUOID_CTRL_0 Register                                                             | 235 |

| Table 11-7  | DMA_IF_RX_RING_SIZE Register                                                              | 236 |

| Table 11-8  | DMA_IF_RX_RING_CNTR Register                                                              | 236 |

| Table 12-1  | Attack Detection Type                                                                     | 238 |

| Table 12-2  | ATK_PRVNT_PORT_EN Register                                                                | 239 |

| Table 12-3  | ATK_PRVNT_CTRL Register                                                                   | 239 |

| Table 12-4  | ATK_PRVNT_ACT Register                                                                    | 240 |

| Table 12-5  | ATK_PRVENT_IPV6_CTRL Register                                                             | 242 |

| Table 12-6  | ATK_PRVENT_ICMP_CTRL Register                                                             | 242 |

| Table 12-7  | ATK_PRVENT_TCP_CTRL Register                                                              | 242 |

| Table 12-8  | ATK_PRVENT_SMURF_CTRL Register                                                            | 242 |

| Table 12-9  | ATK_PRVENT_ARP_INVLD_PORT_ACT Register                                                    | 242 |

| Table 12-10                                                                                                                                  | IP MAC Binding Table Entry                                                                                                                                                                                                                                                                                                                                   | 243                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| Table 12-11                                                                                                                                  | SEC_PORT_IP_MAC_BIND_CTRL Register                                                                                                                                                                                                                                                                                                                           | 245                                                         |

| Table 12-12                                                                                                                                  | SEC_IP_MAC_BIND_CTRL Register                                                                                                                                                                                                                                                                                                                                | 245                                                         |

| Table 13-1                                                                                                                                   | MIR_CTRL Register                                                                                                                                                                                                                                                                                                                                            |                                                             |

| Table 13-2                                                                                                                                   | MIR_SPM_CTRL Register                                                                                                                                                                                                                                                                                                                                        | 247                                                         |

| Table 13-3                                                                                                                                   | MIR_DPM_CTRL Register                                                                                                                                                                                                                                                                                                                                        | 247                                                         |

| Table 13-4                                                                                                                                   | ACL Ingress and Egress Mirror Combination Result                                                                                                                                                                                                                                                                                                             | 247                                                         |

| Table 13-5                                                                                                                                   | MIR_RSPAN_TX_CTRL Register                                                                                                                                                                                                                                                                                                                                   |                                                             |

| Table 13-6                                                                                                                                   | MIR_RSPAN_VLAN_CTRL Register                                                                                                                                                                                                                                                                                                                                 | 249                                                         |

| Table 13-7                                                                                                                                   | MIR_RSPAN_RX_TAG_RM_CTRL Register                                                                                                                                                                                                                                                                                                                            | 250                                                         |

| Table 13-8                                                                                                                                   | MIR_CTRL Register                                                                                                                                                                                                                                                                                                                                            |                                                             |

| Table 13-9                                                                                                                                   | MID CTDI Dogistor                                                                                                                                                                                                                                                                                                                                            | 251                                                         |

| Table 13-10                                                                                                                                  | MIR_CTRL Register                                                                                                                                                                                                                                                                                                                                            | 251                                                         |

| Table 13-11                                                                                                                                  | MIR_CTRL Register                                                                                                                                                                                                                                                                                                                                            | 252                                                         |

| Table 13-12                                                                                                                                  | MTP_CTRL Register                                                                                                                                                                                                                                                                                                                                            | 252                                                         |

| Table 13-13                                                                                                                                  | MIR_CTRL Register  MIR_CTRL Register  MIR_CTRL Register  MTP_CTRL Register  MIR_MODE Register                                                                                                                                                                                                                                                                | 253                                                         |

| Table 13-14                                                                                                                                  | MIR_QID_CTRL Register                                                                                                                                                                                                                                                                                                                                        | 253                                                         |

| Table 13-15                                                                                                                                  | MIR_SAMPLE_RATE_CTRL Register                                                                                                                                                                                                                                                                                                                                | 254                                                         |

| Table 13-16                                                                                                                                  | SFLOW_PORT_RATE_CTRL Register                                                                                                                                                                                                                                                                                                                                | 254                                                         |

| Table 13-17                                                                                                                                  | SFLOW CTRL Register                                                                                                                                                                                                                                                                                                                                          | 255                                                         |

| Table 14-1                                                                                                                                   | OAM PORT ACT CTRI Register                                                                                                                                                                                                                                                                                                                                   | 256                                                         |

| Table 14-2                                                                                                                                   | OAM CTRL Register                                                                                                                                                                                                                                                                                                                                            | 257                                                         |

| Table 14-3                                                                                                                                   | OAM_GBL_DYING_GASP_CTRL Register                                                                                                                                                                                                                                                                                                                             | 257                                                         |

| Table 14-4                                                                                                                                   | OAM_PORT_DYING_GASP_CTRL Register                                                                                                                                                                                                                                                                                                                            | 257                                                         |

| Table 14-5                                                                                                                                   | CFM_RX_LT_CTRL Register                                                                                                                                                                                                                                                                                                                                      | 258                                                         |

| Table 14-6                                                                                                                                   | CFM_RX_LB_CTRL Register                                                                                                                                                                                                                                                                                                                                      | 258                                                         |

| Table 14-7                                                                                                                                   | CFM_RX_CCM_CTRL Register                                                                                                                                                                                                                                                                                                                                     | 258                                                         |

| Table 14-8                                                                                                                                   | CCM_TX_TAG_CTRL Register                                                                                                                                                                                                                                                                                                                                     | 259                                                         |

| Table 14-9                                                                                                                                   | CCM_TX_INST_CTRL Register                                                                                                                                                                                                                                                                                                                                    | 259                                                         |

| Table 14-10                                                                                                                                  | CCM_TX_INST_PKT Register                                                                                                                                                                                                                                                                                                                                     | 260                                                         |

| Table 14-11                                                                                                                                  | CCM_TX_INST_MEM Register                                                                                                                                                                                                                                                                                                                                     | 260                                                         |

| Table 14-12                                                                                                                                  | CCM_TX_INST_TRK_PRESENT Register                                                                                                                                                                                                                                                                                                                             | 260                                                         |

| Table 14-13                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                              |                                                             |

| Table I I IS                                                                                                                                 | CCM RX LIFETIME CTRL Register                                                                                                                                                                                                                                                                                                                                | 260                                                         |

| Table 14-14                                                                                                                                  | CCM_RX_LIFETIME_CTRL Register  CCM_RX_INST_CTRL Register                                                                                                                                                                                                                                                                                                     | 260<br>261                                                  |

|                                                                                                                                              | CCM_RX_LIFETIME_CTRL Register  CCM_RX_INST_CTRL Register  CCM_RX_INST_CNT Register                                                                                                                                                                                                                                                                           | 260<br>261<br>261                                           |

| Table 14-14                                                                                                                                  | CCM_RX_LIFETIME_CTRL Register  CCM_RX_INST_CTRL Register  CCM_RX_INST_CNT Register  ETH_DM_CLK_CTRL Register                                                                                                                                                                                                                                                 | 260<br>261<br>261<br>264                                    |

| Table 14-14<br>Table 14-15                                                                                                                   | CCM_RX_LIFETIME_CTRL Register  CCM_RX_INST_CTRL Register  CCM_RX_INST_CNT Register  ETH_DM_CLK_CTRL Register  ETH_DM_TIME_CTRL_SEC Register                                                                                                                                                                                                                  | 260<br>261<br>261<br>264<br>264                             |

| Table 14-14<br>Table 14-15<br>Table 14-16                                                                                                    | CCM_RX_LIFETIME_CTRL Register  CCM_RX_INST_CTRL Register  CCM_RX_INST_CNT Register  ETH_DM_CLK_CTRL Register  ETH_DM_TIME_CTRL_SEC Register  ETH_DM_TIME_CTRL Register                                                                                                                                                                                       | 260<br>261<br>264<br>264<br>264                             |

| Table 14-14 Table 14-15 Table 14-16 Table 14-17 Table 14-18 Table 14-19                                                                      | CCM_RX_LIFETIME_CTRL Register  CCM_RX_INST_CTRL Register  CCM_RX_INST_CNT Register  ETH_DM_CLK_CTRL Register  ETH_DM_TIME_CTRL_SEC Register  ETH_DM_TIME_CTRL Register  ETH_DM_TIME_CTRL Register                                                                                                                                                            | 260<br>261<br>261<br>264<br>264<br>264                      |

| Table 14-14 Table 14-15 Table 14-16 Table 14-17 Table 14-18                                                                                  | CCM_RX_LIFETIME_CTRL Register  CCM_RX_INST_CTRL Register  CCM_RX_INST_CNT Register  ETH_DM_CLK_CTRL Register  ETH_DM_TIME_CTRL_SEC Register  ETH_DM_TIME_CTRL Register  ETH_DM_TIME_FREQ Register  ETH_DM_TIME_FREQ Register                                                                                                                                 | 260<br>261<br>264<br>264<br>264<br>264                      |

| Table 14-14 Table 14-15 Table 14-16 Table 14-17 Table 14-18 Table 14-19 Table 14-20 Table 14-21                                              | CCM_RX_LIFETIME_CTRL Register  CCM_RX_INST_CTRL Register  CCM_RX_INST_CNT Register  ETH_DM_CLK_CTRL Register  ETH_DM_TIME_CTRL_SEC Register  ETH_DM_TIME_CTRL Register  ETH_DM_TIME_CTRL Register                                                                                                                                                            | 260<br>261<br>264<br>264<br>264<br>264                      |

| Table 14-14 Table 14-15 Table 14-16 Table 14-17 Table 14-18 Table 14-19 Table 14-20 Table 14-21 Table 14-22                                  | CCM_RX_LIFETIME_CTRL Register  CCM_RX_INST_CTRL Register  ETH_DM_CLK_CTRL Register  ETH_DM_TIME_CTRL_SEC Register  ETH_DM_TIME_CTRL Register  ETH_DM_TIME_FREQ Register  ETH_DM_PORT_EN Register  ETH_DM_RX_CTRL Register  ETH_DM_RX_CTRL Register                                                                                                           | 260<br>261<br>264<br>264<br>264<br>265<br>265               |

| Table 14-14 Table 14-15 Table 14-16 Table 14-17 Table 14-18 Table 14-19 Table 14-20 Table 14-21 Table 14-22 Table 15-1                       | CCM_RX_LIFETIME_CTRL Register  CCM_RX_INST_CTRL Register  ETH_DM_CLK_CTRL Register  ETH_DM_TIME_CTRL_SEC Register  ETH_DM_TIME_CTRL Register  ETH_DM_TIME_FREQ Register  ETH_DM_PORT_EN Register  ETH_DM_RX_CTRL Register  ETH_DM_RX_CTRL Register  ETH_DM_RX_TIME Register  STK_GLB_CTRL Register                                                           | 260<br>261<br>264<br>264<br>264<br>265<br>265<br>265        |

| Table 14-14 Table 14-15 Table 14-16 Table 14-17 Table 14-18 Table 14-19 Table 14-20 Table 14-21 Table 14-21 Table 15-1 Table 15-2            | CCM_RX_LIFETIME_CTRL Register  CCM_RX_INST_CTRL Register  ETH_DM_CLK_CTRL Register  ETH_DM_TIME_CTRL_SEC Register  ETH_DM_TIME_CTRL Register  ETH_DM_TIME_FREQ Register  ETH_DM_PORT_EN Register  ETH_DM_RX_CTRL Register  ETH_DM_RX_TIME Register  ETH_DM_RX_TIME Register  STK_GLB_CTRL Register  STK_PORT_ID_CTRL Register                                | 260<br>261<br>264<br>264<br>264<br>265<br>265<br>267        |

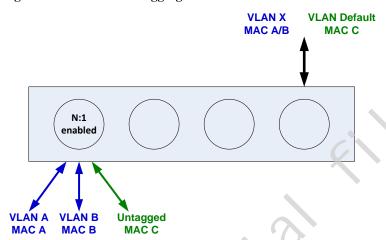

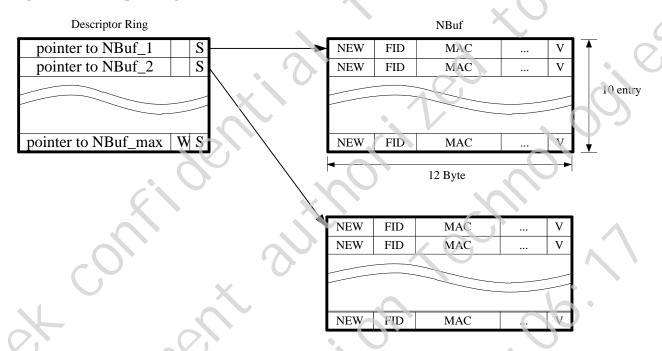

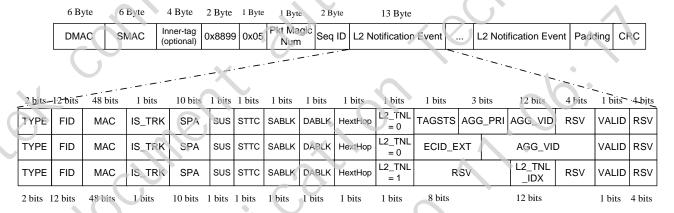

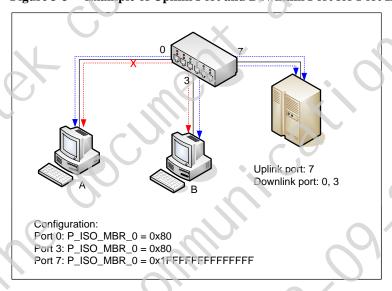

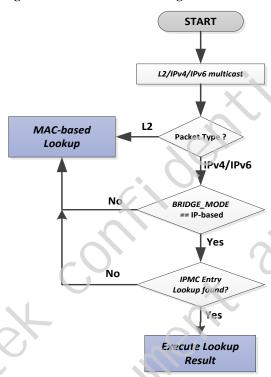

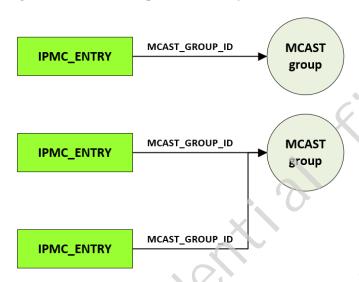

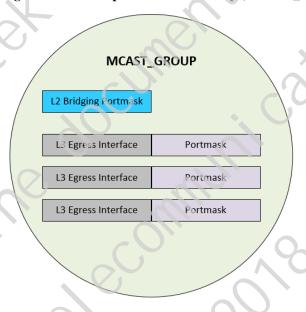

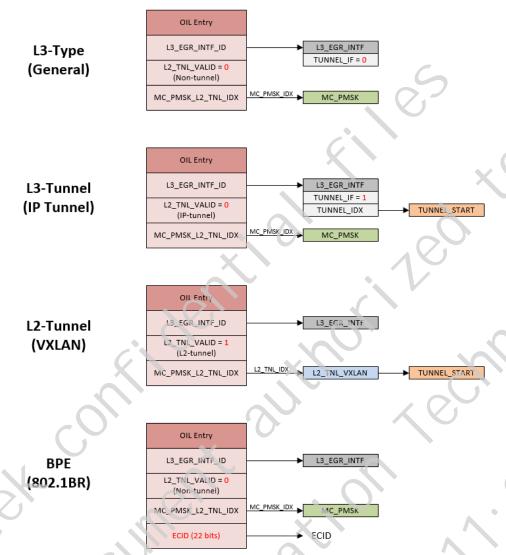

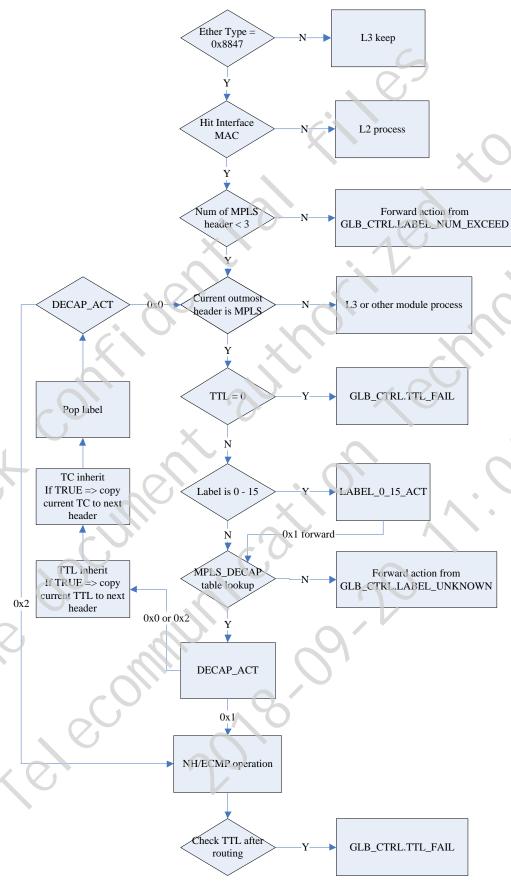

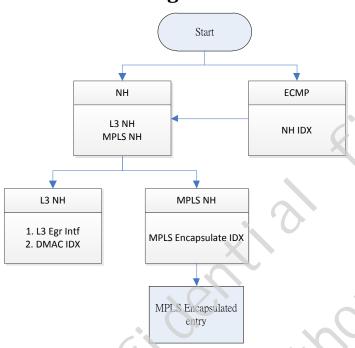

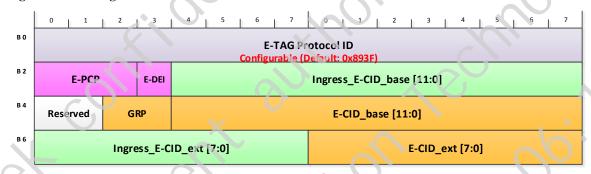

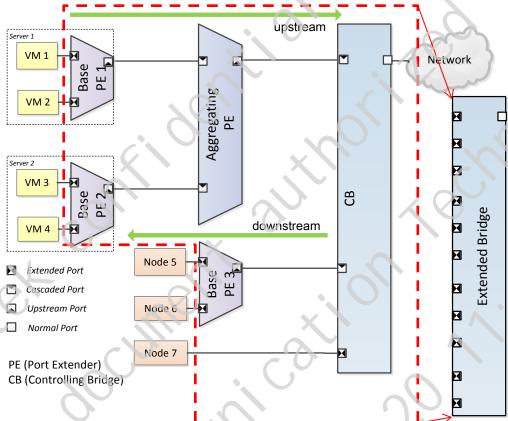

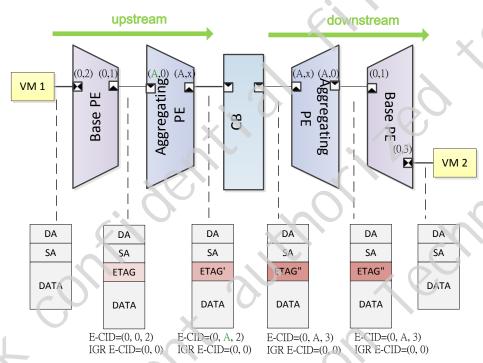

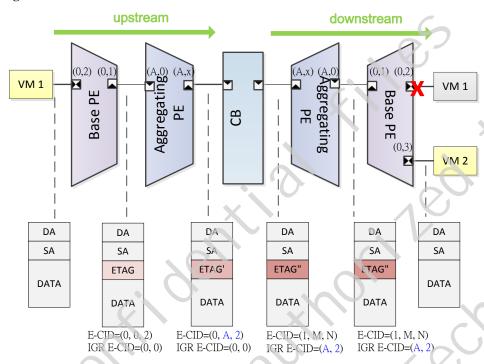

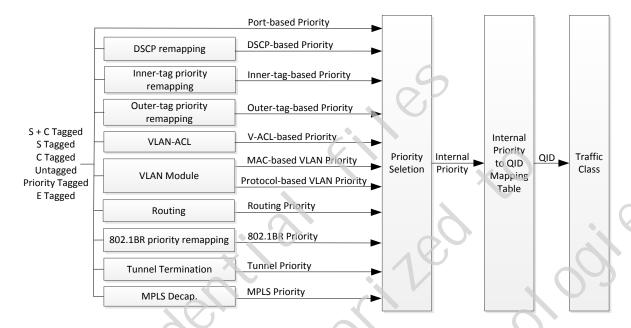

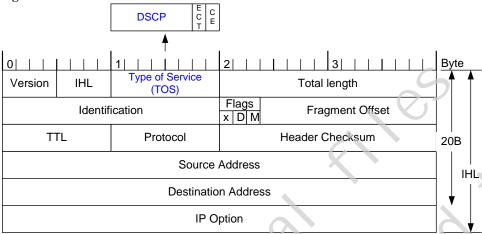

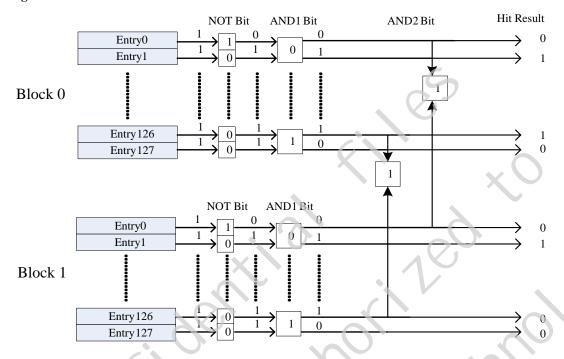

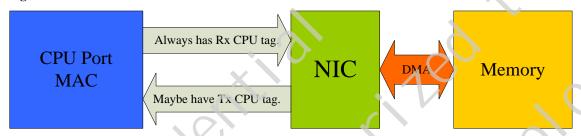

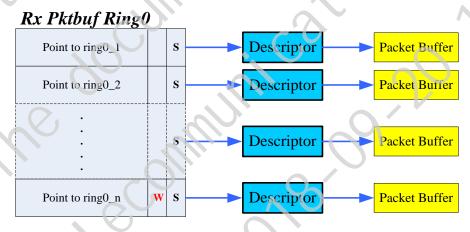

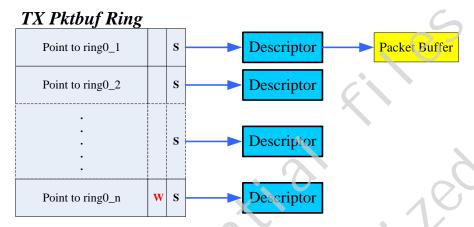

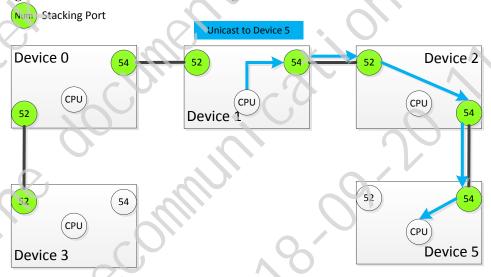

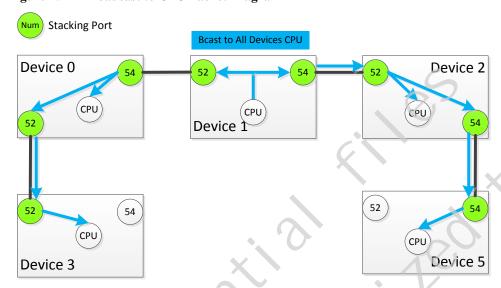

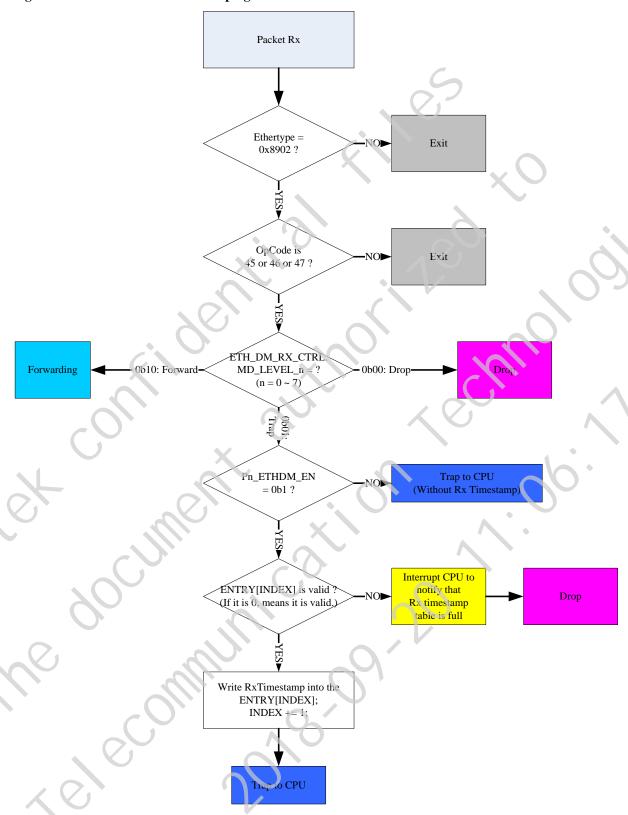

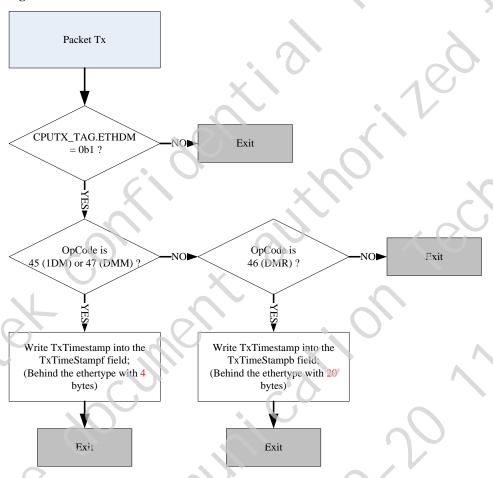

| Table 14-14 Table 14-15 Table 14-16 Table 14-17 Table 14-18 Table 14-19 Table 14-20 Table 14-21 Table 14-22 Table 15-1 Table 15-2 Table 15-3 | CCM_RX_LIFETIME_CTRL Register  CCM_RX_INST_CNT Register  ETH_DM_CLK_CTRL Register  ETH_DM_TIME_CTRL_SEC Register  ETH_DM_TIME_CTRL Register  ETH_DM_TIME_FREQ Register  ETH_DM_PORT_EN Register  ETH_DM_RX_CTRL Register  ETH_DM_RX_CTRL Register  ETH_DM_RX_TIME Register  STK_GLB_CTRL Register  STK_PORT_ID_CTRL Register  STK_DEV_PORT_MAP_CTRL Register | 260<br>261<br>264<br>264<br>264<br>265<br>265<br>267<br>267 |